목적 : AXI-Custom IP를 이용하여 PL의 GPIO핀를 사용한 UART를 제작한다.

* ZC706에서 GPIO핀을 빼기 힘들기 때문에 Zturn Board(ZC702)를 사용했다.

1. 프로젝트 생성 후 Zynq Block를 추가하고, Ztrun의 Configure를 맞춰준다.

(https://github.com/pcw821029/zturn_Study/tree/master/zturn_basic_tcl 에서 다운)

2. Axi-Lite Custom IP를 제작하기 위해 Tools -> Create and Package IP... 를 선택하여 사용자 AXI-IP를 제작한다.

2-1

2-2

2-3

2-4

2-5

3. 추가된 Axi-Lite의 코드 추가

4. 추가된 Axi-Lite S_00_AXI.v 의 코드 추가

4-1

4-2

5. uart 기능을 할 코드 생성

5-1

5-2

5-3

5-4

6. File Groups 부터 Packaging까지 순차적으로 수행한다.

6-1

6-2

6-3

6-4

6-5

6-6

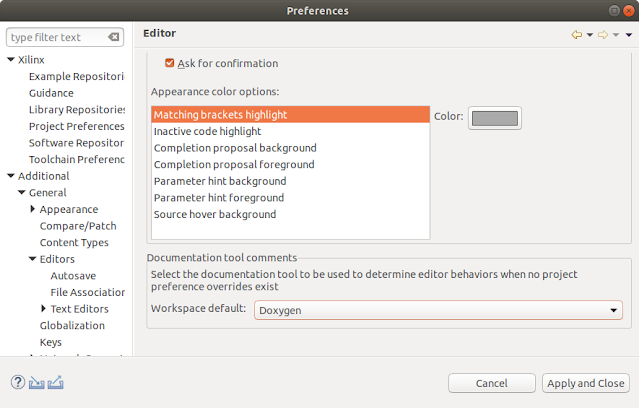

6-7 패키징 하기 전에 Tools->Project Settings..에서 Delete project after packaging의 체크박스를 비활성화 시킨다.

6-8

7. 생성된 IP 불러오기

8. 해당 핀들을 자동으로 연결하고, Zturn 보드의 경우 Address가 0x43C0_0000으로 잡혀있는데 이 영역은 LCD에 뿌려줄 데이터가 기록될 곳이므로 0x4120_0000으로 변경한다.

9. warpper파일을 생성하고, Synthesis까지 수행한다.

10. Run Sysnthesis까지 완료되면 RXD, TXD, RESET핀 맵핑을 하기 위해 open Synthesized Design을 선택하여 핀설정으로 한다.

필자의 경우 J5의 1,2,3핀을 차례데로 1-TXD, 2-RXD, 3-RESET으로 연결 하였다.

J5의 1Pin - T11

J5의 2Pin - U13

J5의 3Pin - T10

11. Implementation 수행, Generate Bitstream까지 수행후 Export H/W 와 Launch SDK를 차례로 수행한다.

12. SDK에서 File->New->Application Project에 Project name을 입력하고 Next를 클릭한다.

12-1

12-2

13. system.mss 파일의 Source탭으로 이동하여 아래와 같이 수정하고 저장한다.

2.4 -> 2.2

14. system.mss 파일의 Overview탭으로 이동하여 Re-generate BSP Sources를 수행한다.

댓글 없음:

댓글 쓰기