* Vivado의 프로젝트 생성및 Block Design 추가는 생략한다.

1. Add IP로 Zynq IP와 AXI GPIO IP 를 추가한다.

2. Zynq IP를 더블클릭하여 Re-customize IP설정을 한다.

a. ZC706 개발 보드를 사용하기 때문에 기본적인 설정은 저장되어 있다. 따라서 이를 선택하면 기본적인 설정은 자동으로 맞춰지며, 추가 적인 부분은 개발자가 추가해주길(ex interrupt 추가)...

3. AXI GPIO 설정

a. 추가된 AXI GPIO를 더블클릭하여 GPIO설정해 준다. (ZC706 Evaluation Kit를 사용하기 때문에 GPIO설정에서 lde 4bits를 선택한다. 이미 준비되어있다.)

4. Zynq와 GPIO를 서로 연결해준다. (비바도 툴에서 자동으로 연결하는 기능이 있다.)

b. Zynq와 GPIO연결된 결과 화면

5. HDL Wrapper 생성

6. Output products 생성

7. Synthesis

b. Pin mapping 정보 (ZC706 Evaluation Kit를 사용하기 때문에 개발자가 따로 설정할 필요없다)

8. Implementation & Bitstream

9. Export Hardware

a. 메뉴에서 File -> Export -> Export Hardware... 선택

b. Include bitstream 체크박스를 선택하고 Ok 클릭

10. Launch SDK

a. 메뉴에서 File -> Launch SDK 선택

11. FSBL 생성

a. 10번에서 Launch SDK를 하게 되면 자동으로 SDK가 실행되는데 SDK 메뉴에서 File -> New -> Application Project를 선택한다.

b. New Project란 팝업창이 뜨면 Project name을 입력하고 Next를 선택한다.

c. Available Templates 에서 Zynq FSBL을 선택후 Finish를 클릭. (FSBL이 만들어지는데는 약간의 시간이 소요된다.)

12. GPIO가 추가됐기 때문에 Devicetree에 해당 GPIO에 대한 정보를 추가해주어야 한다. SDK에서 자동으로 만들어 주기 때문에 크게 문제가 되진않는다.

a. SDK의 메뉴에서 File -> New -> Board Support Package를 선택

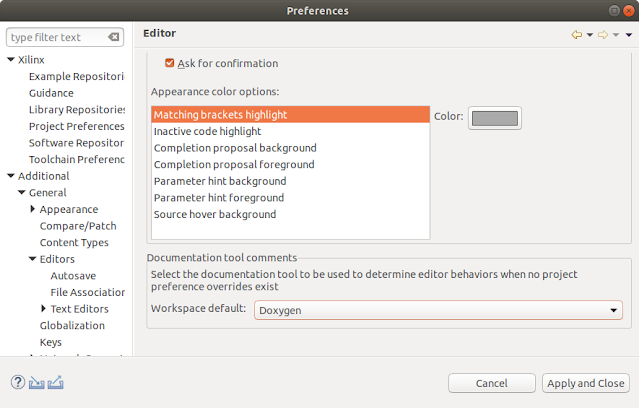

b. New Board Support Package Project 팝업이 뜨면 project name을 입력하고, Board Support Package OS에서 device_tree를 선택하면 된다. ( 처음 설치하면 devicetree리스트가 존재하지 않는다 Xilinx의 Github에 들어가서 devicetree압축 파일을 받아와야 하며 SDK의 설정을 추가적으로 해주어야 한다. 추가 방법은 블로그를 참고하자)

13. 추가된 devicetree에서 필요한 파일은 pl.dtsi파일이며, 이 파일을 리눅스로 옮겨서 devicetree를 다시 컴파일 해주면 된다. (이부분은 AXI GPIO 이용한 LED 제어(PS) 를 참고하자)

댓글 없음:

댓글 쓰기