- H/W 디자인

- ZCU102 Re-customize IP 설정

- PS-PL Configuration

- PS-PL Interface

- Master Interface

- AXI HPM0 FPD : Checked

- AXI HPM0 FPD Data Width : 32

- AXI HPM1 FPD : Checked

- AXI HPM0 FPD Data Width : 128

- AXI HPM0 LPD : Checked

- AXI HPM0 FPD Data Width : 32

- Slave Interface

- AXI HP

- AXI HPC0 FPD : Checked

- AXI HPC0 FPD Data Width : 128

- CDMA IP 코어 추가

- Write/Read Data Width : 128

- Write/Read Burst Size : 4

- Address Width : 32

- 연결

- S_AXI_LITE ----> Zynq AXI HPM0 LPD

- M_AXI ----> Zynq AXI HPC0 FPD

- AXI BRAM Controller IP 코어 추가

- AXI Protocol : AXI4

- Data Width : 128

- Number of BRAM interface : 1

- Enable ECC : No

- Block Memory Genterator IP 코더 추가

- Basic

- Mode : BRAM Controller

- Memory Type : True Dual Port RAM

- Other Options

- Enable Safety Circuit : UnChecked

- ㅇㅇ

2019년 6월 13일 목요일

ZCU102 CDMA with BRAM

피드 구독하기:

댓글 (Atom)

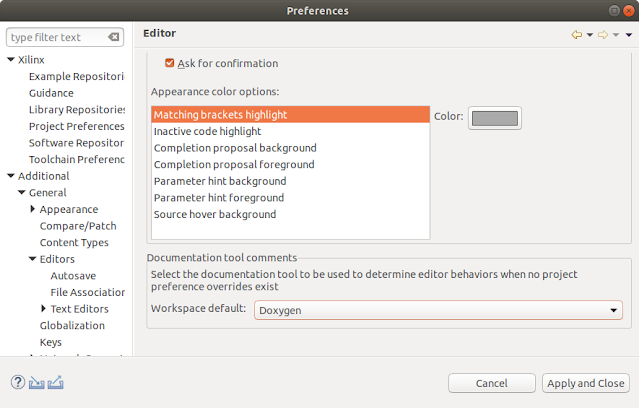

VITIS Git + Doxygen Config

Doxygen Configure 1. Vitis 메뉴의 Window->Preference의 C/C++ -> Editor의 Documentation tool comments 기본 설정값을 Doxygen으로 변경 설정 후 함수 바로 위에서 /...

-

1. 커널 소스(드라이버 소스파일)수정 PetaLinux을 빌드한 후 생성된 이미지는 <plnx-proj-root>/image/linux에 있으며, 커널 소스는 <plnx-proj-root>/build/tmp/work-...

-

목적 : 비바도에서 제공하는 IP core인 AXI BRAM Controller 2개와 실제 메모리 역할을 하는 Block Memory Generator(True Dual Port RAM)를 사용하여 axi_bram_ctrl_0을 통해 PORTA에 ...

-

우선 PetaLinux설치를 위해 필요한 파일들을 Xilinx에서 다운 받는다. 보드는 ZCU102를 사용하기 때문에 설정에 필요한 xilinx-zcu102-v2017.3-final.bsp 파일과 설치를 위한 petalinux-v2017.3-fi...

댓글 없음:

댓글 쓰기